심사관 :

최규돈

## (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.) *H03K 3/57* (2006.01) *H03K 5/134* (2014.01)

(52) CPC특허분류 *H03K 3/57* (2013.01) *H03K 3/64* (2013.01)

(21) 출원번호 10-2019-0078107

(22) 출원일자 2019년06월28일 심사청구일자 2019년06월28일

(56) 선행기술조사문헌 JP2006229853 A\* KR101298179 B1\* KR1020080052285 A\* KR1020090028286 A\* \*는 심사관에 의하여 인용된 문헌 (45) 공고일자 2020년06월17일

(11) 등록번호 10-2123999

(24) 등록일자 2020년06월11일

(73) 특허권자한발대학교 산학협력단대전광역시 유성구 동서대로 125 (덕명동)

(72) 발명자 김주성

마하무드 하피즈 우스만

(뒷면에 계속)

(74) 대리인 특허법인 플러스

전체 청구항 수 : 총 5 항

(54) 발명의 명칭 초광대역 펄스 생성 장치

#### (57) 요 약

본 발명은 복수 개의 딜레이 셀이 특정 시간 구간에 따라 복수 개의 트랜지스터에 구형파 전압을 제공하고, 복수 개의 트랜지스터는 발진기에 상기 특정 시간 구간에 따라 전류를 전달하며, 발진기는 상기 전류를 전달 받아 지수함수적으로 감쇠되는 복수 개의 정현파 전압을 생성하여, 출력단에서 초광대역 펼스가 출력되도록 구성되어 있다. 이러한 본 발명에 의하면, 초광대역 펄스 생성 장치에서 생성된 초광대역 펄스의 사이드로브가 FCC(Federal Communication Commission) 스펙트럼 마스크를 넘지 않도록 억압되기 때문에, FCC 스펙트럼 마스크에 부합할 수 있게 된다.

### 대표도

(52) CPC특허분류

#### **HO3K 5/134** (2015.01)

(72) 발명자

#### 한석균

이상국

이 발명을 지원한 국가연구개발사업

과제고유번호 1711081044

부처명 과학기술정보통신부

연구관리전문기관 정보통신기술진흥센터

연구사업명 방송통신산업기술개발사업

연구과제명 뇌신호 처리 및 무선 전송을 위한 뇌삽입용 bio-telemetry 플랫폼 구현

기 여 율 1/1

주관기관 충남대학교 산학협력단 연구기간 2018.01.01 ~ 2018.12.31

#### 명 세 서

### 청구범위

#### 청구항 1

입력 받은 스텝 전압을 구형파 전압으로 전환하는 복수 개의 딜레이 셀;

상기 복수 개의 딜레이 셀 각각에 의해 전환된 구형파 전압을 입력 전압으로 하여 전류를 생성하는 복수 개의 트랜지스터;

상기 복수 개의 트랜지스터 각각에 의해 생성된 전류를 전달 받아 지수함수적으로 감쇠되는 복수 개의 정현파 전압을 생성하는 발진기; 및

상기 복수 개의 트랜지스터 및 상기 발진기와 연결되며, 상기 발진기에서 생성되는 복수 개의 정현파 전압을 합성하여 초광대역 펄스를 출력하는 출력단;을 포함하며,

상기 복수 개의 딜레이 셀 각각은 상기 스텝 전압을 소정 시간만큼 지연시켜 이웃하는 딜레이 셀에 지연된 스텝 전압을 출력하거나,

상기 복수 개의 딜레이 셀 각각은 상기 지연된 스텝 전압을 이웃하는 딜레이 셀로부터 입력 받고,

상기 복수 개의 딜레이 셀 각각은 인버터를 이용하여 상기 스텝 전압을 소정 시간만큼 지연시키며,

상기 복수 개의 딜레이 셀 각각은 상기 인버터 및 앤드 게이트를 이용하여 상기 스텝 전압을 상기 구형파 전압으로 전환하는 것을 특징으로 하는 초광대역 펄스 생성 장치.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

삭제

#### 청구항 5

제1항에 있어서,

상기 복수 개의 트랜지스터는 상기 복수 개의 딜레이 셀과 1:1로 대응되도록 연결된 것을 특징으로 하는 초광대 역 펄스 생성 장치.

#### 청구항 6

제5항에 있어서,

상기 출력단에서 출력되는 초광대역 펄스의 형태는 상기 복수 개의 트랜지스터 각각에서 생성되는 전류의 크기에 따라 달라지는 것을 특징으로 하는 초광대역 펄스 생성 장치.

#### 청구항 7

제1항에 있어서,

상기 발진기는 서로 병렬 연결된 저항, 인덕터 및 커패시터를 포함하는 초광대역 펄스 생성 장치.

#### 청구항 8

제1항에 있어서.

상기 출력단에는 상기 초광대역 펄스에서 DC 성분을 제거하기 위하여 바이패스 커패시터가 연결되어 있는 것을 특징으로 하는 초광대역 펄스 생성 장치.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 초광대역(ultra-wideband; UWB) 통신에 필요한 초광대역 펼스 생성 장치에 관한 것이다.

#### 배경기술

- [0002] 근거리 통신용으로 현재 활발히 사용되고 있는 블루투스 기술은 사용자가 많을 경우 실시간 전송이 원활하게 이루어지지 못하며, 통신 프로토콜이 복잡하고 전력 소모가 크기 때문에 장시간 사용에 어려움을 가지고 있다.

- [0003] 이에 따라 이를 극복하기 위한 통신 방식들이 제안되고 있는데, 이중에서도 2002년 4월 미국 연방통신위원회 (Federal Communication Commission; FCC)의 주파수 할당 및 상업화 승인 이후, 초광대역 통신 기술에 대한 연구와 개발이 전 세계적으로 활발히 진행되고 있다. 2007년 IEEE 802.15.4a 국제 표준화 그룹에서는 무선 측위 기능까지 수반하는 저속 저전력 W-PAN(Wireless Personal Area Network)용 UWB 표준화를 제정하여 상용화 제품 개발에 속도를 더하고 있다.

- [0004] 연속적인 정현파를 사용하는 기존의 무선통신 시스템과는 달리, 임펄스 라디오 UWB(Impulse Radio UWB; IR-UWB) 시스템의 송신단에서는 1nsec 내외의 매우 좁은 폭을 갖는 펄스 혹은 가우시안 모노사이클 펄스(Gaussian monocycle pulse)를 단속적으로 전송한다. 초광대역 펄스 생성 장치는 단거리 구간에서 낮은 전력으로 넓은 스펙트럼 주파수를 통하여 많은 양의 디지털 데이터를 전송하기 위한 것으로서, 허가 받은 상용의 대역폭 신호를 해치지 않기 위해 미국 연방통신위원회에서 규약하는 스펙트럼 마스크(즉, FCC 스펙트럼 마스크)를 만족하여야 한다.

- [0005] 종래 초광대역 펄스 생성 장치 중에는 생성한 펄스의 전력 스펙트럼 밀도(power spectral density; PSD)가 FCC 스펙트럼 마스크에 부합시키기 위하여 대역 통과 필터를 이용한 것이 있다. 하지만, 이러한 펄스 생성 장치는 펄스의 형태 및 지속이 대역 통과 필터의 과도 응답 특성에 좌우됨으로써 원하는 형태의 펄스 생성이 용이하지 않고, 송신단 안테나와의 인터페이스를 위한 임피던스 정합 회로가 추가적으로 필요하다는 문제점이 있다.

- [0006] 또한, 종래 초광대역 펄스 생성 장치 중에는 차동 구조를 채택하고, 상기 차동 구조의 차동 출력과 최종 단일 출력의 인터페이스를 위해 밸룬(balun)을 이용한 것이 있다. 하지만, 이러한 펄스 생성 장치는 추가적인 밸룬을 필요로 하기 때문에 에너지 효율이 떨어진다는 문제점이 있다. 또한, 원하는 펄스 개수에 따라 다상 클럭 (multiphase clock)의 생성 및 분배가 필요하여, 전력 소모가 크고 시스템 역시 커진다는 문제점이 있다.

#### 선행기술문헌

#### 특허문헌

[0007] (특허문헌 0001) 공개특허공보 제2010-0068809호

#### 발명의 내용

#### 해결하려는 과제

[0008] 본 발명은 상기와 같은 문제점을 해결하기 위하여 안출된 것으로서, FCC 스펙트럼 마스크에 부합하면서도, 원하는 형태의 펄스를 용이하게 생성할 수 있는 초광대역 펄스 생성 장치를 제공하는 것에 그 목적이 있다.

[0009] 또한, 본 발명은 저전력 동작이 가능하고, 저가로 구현할 수 있으면서도, 에너지 효율은 상승시킬 수 있는 초광 대역 펄스 생성 장치를 제공하는 것에 그 목적이 있다.

#### 과제의 해결 수단

- [0010] 상기와 같은 목적을 달성하기 위하여, 본 발명에 따른 초광대역 펄스 생성 장치는, 입력 받은 스텝 전압을 구형 파 전압으로 전환하는 복수 개의 딜레이 셀; 상기 복수 개의 딜레이 셀 각각에 의해 전환된 구형파 전압을 입력 전압으로 하여 전류를 생성하는 복수 개의 트랜지스터; 상기 복수 개의 트랜지스터 각각에 의해 생성된 전류를 전달 받아 지수함수적으로 감쇠되는 복수 개의 정현파 전압을 생성하는 발진기; 및 상기 복수 개의 트랜지스터 및 상기 발진기와 연결되며, 상기 발진기에서 생성되는 복수 개의 정현파 전압을 합성하여 초광대역 필스를 출력하는 출력단을 포함한다.

- [0011] 여기서, 상기 복수 개의 딜레이 셀 각각은 상기 스텝 전압을 소정 시간만큼 지연시켜 이웃하는 딜레이 셀에 지연된 스텝 전압을 출력하거나, 상기 복수 개의 딜레이 셀 각각은 상기 지연된 스텝 전압을 이웃하는 딜레이 셀로부터 입력 받을 수 있다.

- [0012] 그리고 상기 복수 개의 딜레이 셀 각각은 인버터를 이용하여 상기 스텝 전압을 소정 시간만큼 지연시킬 수 있다.

- [0013] 또한, 상기 복수 개의 딜레이 셀 각각은 상기 인버터 및 앤드 게이트를 이용하여 상기 스텝 전압을 구형파 전압으로 전환할 수 있다.

- [0014] 또한, 상기 복수 개의 트랜지스터는 상기 복수 개의 딜레이 셀과 1:1로 대응되도록 연결될 수 있다.

- [0015] 그리고 상기 출력단에서 출력되는 초광대역 필스의 형태는 상기 복수 개의 트랜지스터 각각에서 생성되는 전류 의 크기에 따라 달라지는 것을 특징으로 한다.

- [0016] 상기 발진기는 서로 병렬 연결된 저항, 인덕터 및 커패시터를 포함한 것일 수 있다.

- [0017] 그리고 상기 출력단에는 상기 초광대역 펄스에서 DC 성분을 제거하기 위하여 바이패스 커패시터가 연결될 수 있다.

#### 발명의 효과

- [0018] 본 발명은 복수 개의 딜레이 셀이 특정 시간 구간에 따라 복수 개의 트랜지스터에 구형파 전압을 제공하고, 복수 개의 트랜지스터는 발진기에 상기 특정 시간 구간에 따라 전류를 전달하며, 발진기는 상기 전류를 전달 받아 지수함수적으로 감쇠되는 복수 개의 정현파 전압을 생성하여, 출력단에서 초광대역 펄스가 출력되도록 구성되어 있다. 이러한 본 발명에 의하면, 초광대역 펄스 생성 장치에서 생성된 초광대역 펄스의 사이드로브가 FCC 스펙트럼 마스크를 넘지 않도록 억압되기 때문에, FCC 스펙트럼 마스크에 부합할 수 있게 된다.

- [0019] 또한, 본 발명에 의하면, 발진기를 구성하는 저항, 인덕터 및 커패시터의 합성 임피던스를 조정하는 것만으로도 초광대역 펄스 스펙트럼의 중심 주파수를 가변할 수 있기 때문에, 원하는 형태의 펄스를 손쉽게 생성할 수 있다.

- [0020] 또한, 본 발명에 의하면, 별도의 임피던스 매칭 회로를 구비하지 않더라도 발진기를 통해 안테나와의 임피던스 매칭을 손쉽게 수행할 수 있다. 게다가, 본 발명은 별도의 밸룬이나 임피던스 매칭 회로가 필요하지 않을 뿐 아니라, 복수 개의 딜레이 셀에서 생성하는 디지털 펄스를 통해 초광대역 펄스를 생성하기 때문에, 장치의 저전력 동작이 가능하고, 저가로 구현할 수 있으며, 에너지 효율 또한 상승시킬 수 있게 된다.

#### 도면의 간단한 설명

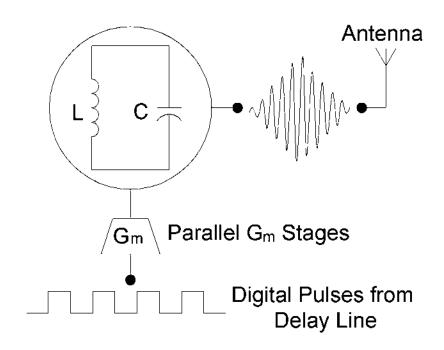

[0021] 도 1은 LC 탱크를 기반으로 한 발진기를 이용하여 초광대역 펄스를 생성하는 원리를 설명하기 위한 도면이다.

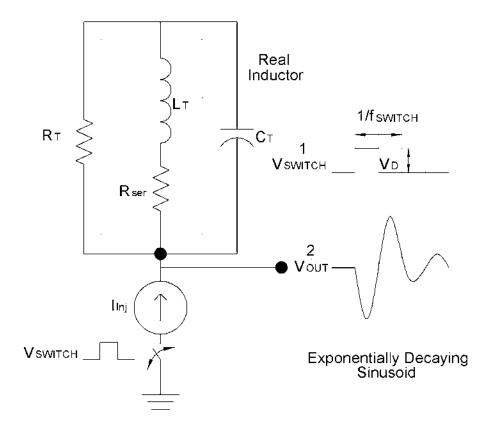

도 2는 본 발명에서 이용하는 RLC 탱크 기반 발진기의 출력 전압 생성 원리를 설명하기 위한 도면이다.

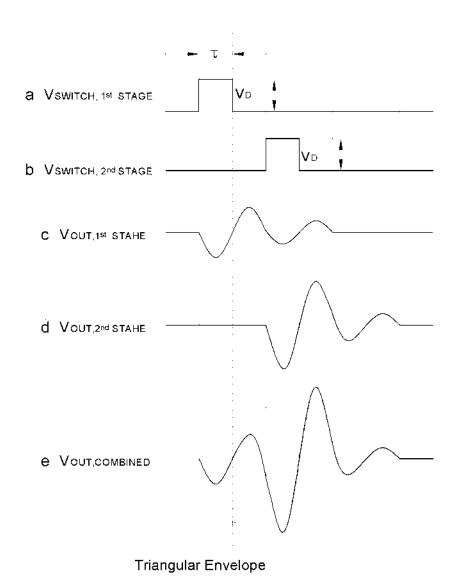

도 3은 도 2에 나타낸 발진기에서 생성된 출력 전압의 합성으로 인해 삼각형의 포락선 펄스가 생성되는 모습을 나타낸 도면이다.

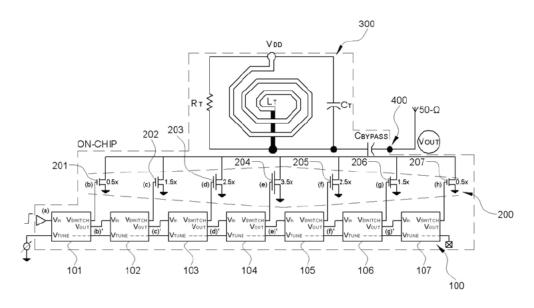

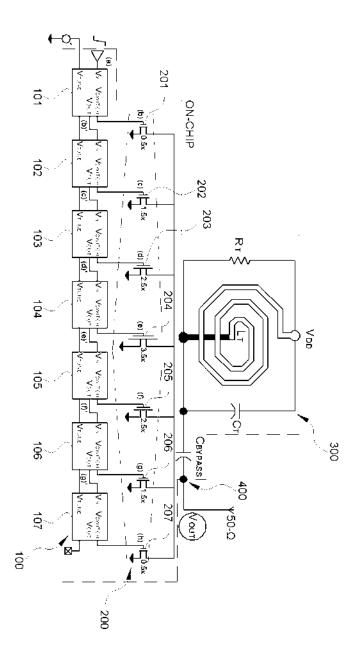

도 4는 본 발명의 일 실시예에 따른 초광대역 펄스 생성 장치를 나타낸 도면이다.

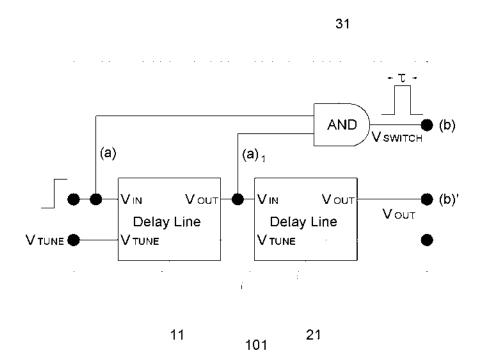

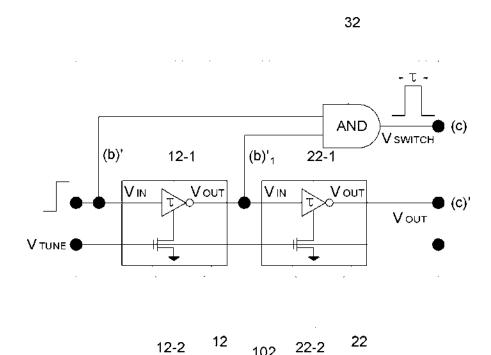

- 도 5는 도 4에 나타낸 딜레이 셀의 내부 구조를 나타낸 도면이다.

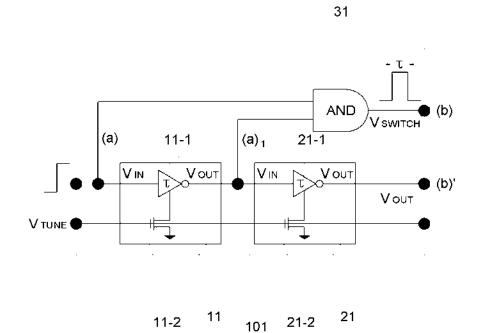

- 도 6은 도 4에 나타낸 복수 개의 딜레이 셀 중 제1 딜레이 셀을 나타낸 도면이다.

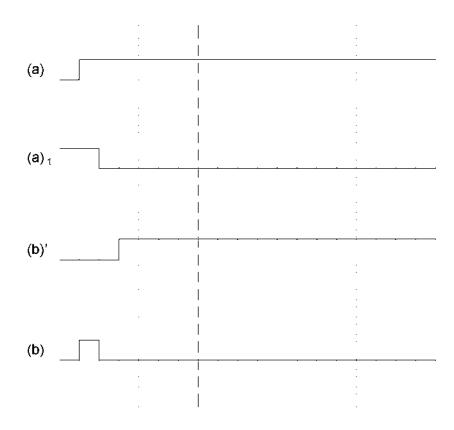

- 도 7은 도 6에 나타낸 딜레이 셀의 각 구역에 대한 타이밍 다이아그램이다.

- 도 8은 도 4에 나타낸 복수 개의 딜레이 셀 중 제2 딜레이 셀을 나타낸 도면이다.

- 도 9는 도 8에 나타낸 딜레이 셀의 각 구역에 대한 타이밍 다이아그램이다.

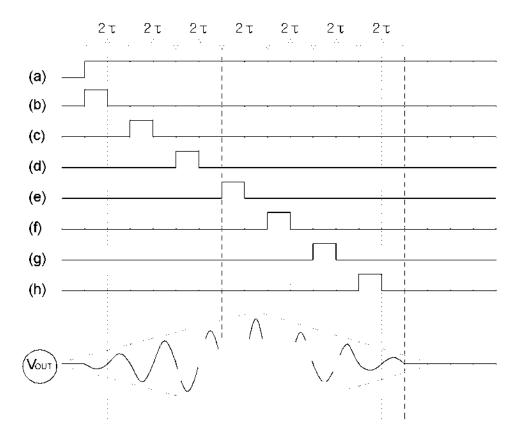

- 도 10은 도 4에 나타낸 초광대역 펄스 생성 장치의 각 구역에 대한 타이밍 다이아그램이다.

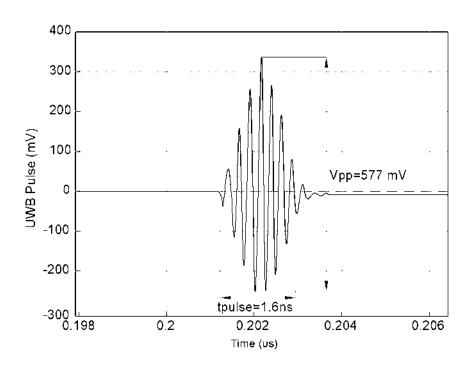

- 도 11은 도 4에 나타낸 장치를 통해 생성한 초광대역 펄스의 시뮬레이션 결과이다.

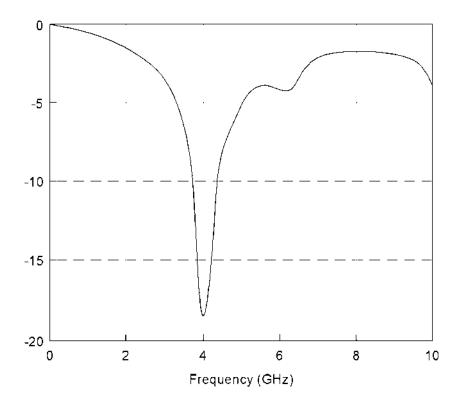

- 도 12는 도 4에 나타낸 장치를 안테나의 임피던스와 매칭시킨 시뮬레이션 결과이다.

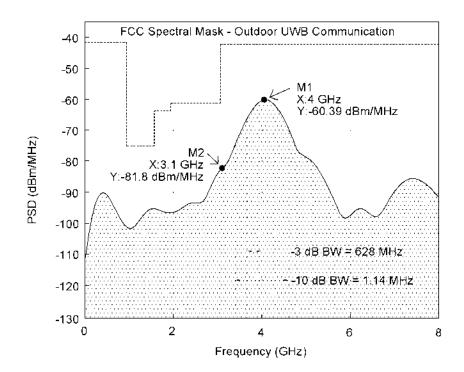

- 도 13은 도 11에 나타낸 초광대역 펄스의 전력 스펙트럼 밀도에 관한 시뮬레이션 결과이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0022] 이하, 첨부한 도면들을 참조하여 본 발명에 따른 초광대역 펄스 생성 장치에 대해 상세하게 설명한다. 첨부한 도면들은 통상의 기술자에게 본 발명의 기술적 사상이 충분히 전달될 수 있도록 하기 위하여 어디까지나 예시적으로 제공되는 것으로서, 본 발명은 이하 제시되는 도면들로 한정되지 않고 다른 형태로 얼마든지 구체화될 수 있다.

- [0023] 본 발명에 따른 초광대역 펄스 생성 장치에 대해 설명하기 전에, 먼저 도 1 내지 도 3을 참조하여 본 발명에서 초광대역 펄스를 생성하는 원리에 대해 설명하기로 한다.

- [0024] 다중 대역 IR-UWB 시스템에서의 펄스는 단일 대역 시스템에서의 펄스에 비해 긴 지속 시간(duration)을 가지며, 복수 개의 정현파들로 이루어진다. 다중 대역 IR-UWB 시스템에서의 펄스는 발진기의 진폭을 조정함으로써 생성되며, 이로 인해 직사각형(rectangular), 삼각형(triangular), 사인형(sine) 등과 같은 형태의 펄스 포락선을 가질 수 있게 된다. 그리고 발진기의 중심 주파수는 펄스 스펙트럼의 중심 주파수를 정의한다.

- [0025] 펄스 포락선의 형태에 따라 펄스 스펙트럼은 상이한 사이드로브(sidelobe) 억압 기능을 제공한다. 여기서, 사이드로브 억압 기능은 펄스 스펙트럼에서 메인로브(main lobe)와 사이드로브 간의 차이를 의미한다. 예를 들어, 직사각형의 포락선 펄스는 약 12.86dB의 사이드로브 억압 기능을 제공하고, 삼각형의 포락선 펄스는 약 26.61dB의 사이드로브 억압 기능을 제공하며, 사인형의 포락선 펄스는 약 23dB의 사이드로브 억압 기능을 제공한다. 사이드로브 억압 기능은 미국 연방통신위원회(FCC)에서 할당한 주파수와 관련이 있다. 즉, 초광대역 펄스 생성 장치로 생성한 펄스의 전력 스펙트럼 밀도(PSD)가 FCC 스펙트럼 마스크에 부합하기 위해서는 사이드로브 억압 기능이 클수록 유리하다.

- [0026] 또한, 직사각형의 포락선 펄스나 사인형의 포락선 펄스를 생성하는 것에 비해 삼각형의 포락선 펄스를 생성하는 것이 장치의 전력 소모나 에너지 효율 측면에서 유리할 수 있다. 이에 따라, 이하에서는 도 1에 나타낸 바와 같은 삼각형의 포락선 펄스를 생성하는 방법에 대해 설명하기로 하되, 삼각형의 포락선 펄스를 생성하는 방법은 직사각형, 사인형 기타 다른 형상의 포락선 펄스를 생성하는 경우에도 마찬가지로 적용될 수 있다.

- [0027] 도 1은 LC 탱크를 기반으로 한 발진기를 이용하여 초광대역 펄스를 생성하는 원리를 설명하기 위한 도면이다.

- [0028] 도 1에 나타낸 바와 같이, 삼각형의 포락선 펄스는 LC 탱크를 기반으로 한 발진기의 발진 진폭(oscillation amplitude)의 양을 트랜스컨덕터(transconductor; Gm)를 통해 제어함으로써 생성될 수 있다. 본 발명에서는 트랜스컨덕터(Gm)가 서로 병렬 연결된 복수 개의 트랜지스터로 이루어질 수 있으며, 각 트랜지스터는 선형적으로 변하는 트랜스컨덕턴스를 갖는다.

- [0029] 트랜스컨덕터(Gm)의 입력단에는 구형파의 디지털 필스가 입력되며, 이때 상기 구형파의 디지털 필스는 케스케이드(cascade) 결합된 딜레이 라인(delay lines)에서 생성될 수 있다. 여기서, 상기 딜레이 라인은 인버터를 기반으로 하여 제작될 수 있다. 그리고 상기 딜레이 라인의 전파 딜레이(propagation delay) 및 상기 LC 탱크의 발진 주파수를 튜닝함에 따라, 원하는 형상의 삼각 포락선을 갖는 초광대역 필스를 생성할 수 있다.

- [0030] 도 2는 본 발명에서 이용하는 RLC 탱크 기반 발진기의 출력 전압 생성 원리를 설명하기 위한 도면이다.

- [0031] 도 2의 좌측에 나타낸 RLC 탱크 기반 발진기는 저항 $(R_T)$ , 인덕터 $(L_T)$  및 커패시터 $(C_T)$ 가 서로 병렬 연결되도록

구성되며, 인덕터의 기생 저항( $R_{ser}$ )은 인덕터( $L_T$ )와 직렬 연결되도록 구성된다. 여기서, RLC 탱크에 전달되는 에너지는 스위칭 전압( $V_{SWITCH}$ )의 스위칭 주파수( $f_{SWITCH}$ )에 의존하는 전류( $I_{ini}$ ) 형태이다.

- [0032] 도 2의 우측에 나타낸 그래프 ①, ②에서 x축은 시간을, y축은 전압을 나타낸다. 그래프 ①은 스위칭 전압 (Vswirch)을 나타낸 것이고, 그래프 ②는 RLC 탱크 기반 발진기의 출력 전압을 나타낸 것이다.

- [0033] 구형파 형태의 스위칭 전압(V<sub>SWITCH</sub>)에 따라 RLC 탱크에 전류(I<sub>inj</sub>)가 전달될 경우, 상기 RLC 탱크의 자연 응답 (natural response)은 다음의 수학식 1과 같이 2차 미분 방정식 형태로 나타낼 수 있다.

- [0034] [수학식 1]

$$\frac{d^2V_{OUT}(t)}{dt^2} + 2\alpha \frac{dV_{OUT}(t)}{dt} + \omega_o^2V_{OUT}(t) = 0$$

- [0036] 상기 수학식 1에서 Vour(t)는 RLC 탱크 기반 발진기의 출력 전압이고,  $\alpha = \frac{1}{2R_{eo}C_T} = \frac{1}{2(R_T \parallel R_{oer})C_T}$  이며,  $\omega_o = \frac{1}{2\pi\sqrt{L_TC_T}}$  이다.

- [0037] 그리고 상기 수학식 1에서 α<ω。(즉, underdamped system)라고 가정하면, 상기 수학식 1의 해는 다음의 수학식 2와 같이 나타낼 수 있다.

- [0038] [수학식 2]

- [0039]  $V_{OUT}(t) \approx V_p e^{-\alpha t} \sin(\omega_o t + \phi)$

- [0040] 상기 수학식 2에서 V₂는 출력 전압의 진폭을, ∅는 출력 전압의 위상을 나타낸다. 상기 수학식 2 및 그래프 ②에서 알 수 있듯이, RLC 탱크 기반 발진기의 출력 전압은 지수함수적으로 감쇠되는 정현파 형태를 갖는다.

- [0041] 도 3은 도 2에 나타낸 발진기에서 생성된 출력 전압의 합성으로 인해 삼각형의 포락선 펄스가 생성되는 모습을 나타낸 도면이다. 도 3에서 x축은 시간을, y축은 전압을 나타낸다.

- [0042] 도 3@에 나타낸 구형파 형태의 스위칭 전압(V<sub>SWITCH, IST STAGE</sub>)은 시간  $\tau (=\frac{1}{2f_{SWITCH}})$  동안만 온(on) 상태이며, 도 3ⓒ는 도 3@에 나타낸 구형파 형태의 스위칭 전압(V<sub>SWITCH, IST STAGE</sub>)에 따라 RLC 탱크 기반 발진기에 전류(I<sub>inj,a</sub>)가 전달될 경우, RLC 탱크 기반 발진기의 출력 전압을 나타낸 것이다.

- [0043] 도 3⑤에 나타낸 구형과 형태의 스위칭 전압(V<sub>SWITCH,2nd STAGE</sub>) 역시 시간 <sup>τ(= 1</sup>2f swince)</sup> 동안만 온(on) 상태이며, 다만 도 3⑥에 나타낸 구형과 형태의 스위칭 전압(V<sub>SWITCH,2nd STAGE</sub>)은 도 3億에 나타낸 구형과 형태의 스위칭 전압(V<sub>SWITCH,1st STAGE</sub>)에 비해 2 τ 만큼의 시간 딜레이가 존재한다. 그리고 도 3億는 도 3⑥에 나타낸 구형과 형태의 스위칭 전압(V<sub>SWITCH,2nd STAGE</sub>)에 따라 RLC 탱크 기반 발진기에 전류(I<sub>inj,b</sub>)가 전달될 경우, RLC 탱크 기반 발진기의 출력 전압을 나타낸 것이다.

- [0044] 도 3ⓒ 및 도 3ⓓ에서 알 수 있듯이, RLC 탱크 기반 발진기의 출력 전압(V<sub>OUT,1ST STAGE</sub>, V<sub>OUT,2ND STAGE</sub>)은 지수함수적으로 감쇠되는 정현과 형태를 갖는다. 다만, 스위칭 전압(V<sub>SWITCH,2nd STAGE</sub>)은 스위칭 전압(V<sub>SWITCH,1ST STAGE</sub>)에 비해 2 τ 만큼의 시간 딜레이가 존재하기 때문에, 출력 전압(V<sub>OUT,2ND STAGE</sub>)의 온(ON) 시점은 출력 전압(V<sub>OUT,1ST STAGE</sub>)의 온시점에 비해 2 τ 만큼의 시간 딜레이가 존재한다.

- [0045] 그리고 도 3億에 나타낸 출력 전압(V<sub>OUT, 2ND STAGE</sub>)은 도 3ⓒ에 나타낸 출력 전압(V<sub>OUT, IST STAGE</sub>)에 비해 전체적으로 진 폭(V<sub>p</sub>)이 더 크다. 이는 도 3ⓒ에서 RLC 탱크 기반 발진기에 전달되는 전류(I<sub>inj,a</sub>)에 비해, 도 3億에서 RLC 탱크 기반 발진기에 전달되는 전류(I<sub>inj,b</sub>)를 더 크게 하였기 때문이다(즉, I<sub>inj,a</sub> < I<sub>inj,b</sub>).

- [0046] 한편, 도 3ⓒ는 도 3ⓒ에 나타낸 출력 전압(V<sub>OUT, IST</sub> STAGE)과 도 3ⓓ에 나타낸 출력 전압(V<sub>OUT, 2ND</sub> STAGE)을 합성한 출

력 전압 $(V_{OUT,COMBINED})$ 을 나타낸 것이다. 도 3ⓒ에 나타낸 바와 같이, 도 3ⓒ에 나타낸 출력 전압 $(V_{OUT,IST\ STAGE})$ 과 도 3ⓒ에 나타낸 출력 전압 $(V_{OUT,2ND\ STAGE})$ 을 합성할 경우 삼각형의 포락선 펄스를 생성할 수 있으며, 이와 같이 생성한 삼각형의 포락선 펄스는 FCC 스펙트럼 마스크의 전력 스펙트럼 밀도(PSD)를 넘지 않도록 펄스 스펙트럼의 사이드로브 억압 기능을 제공할 수 있다.

- [0047] 도 4는 본 발명의 일 실시예에 따른 초광대역 펄스 생성 장치를 나타낸 도면이다. 도 4에 나타낸 바와 같이, 본 발명의 일 실시예에 따른 초광대역 펄스 생성 장치는 복수 개의 딜레이 셀(100), 복수 개의 트랜지스터(200), 발진기(300) 및 출력단(400)을 포함한다.

- [0048] 복수 개의 딜레이 셀(100)은 입력 받은 스텝 전압을 구형파 전압으로 전환한다. 여기서, 복수 개의 딜레이 셀(100) 중 가장 좌측에 위치한 딜레이 셀(101)은 외부로부터 스텝 전압을 입력 받으며, 나머지 딜레이 셀(102~107)은 이웃하는 딜레이 셀(101~106)로부터 스텝 전압을 입력 받는다.

- [0049] 도 5는 도 4에 나타낸 딜레이 셀의 내부 구조를 나타낸 도면이다. 도 5는 복수 개의 딜레이 셀(100) 중 가장 좌 측에 위치한 딜레이 셀(101)을 나타낸 것이지만, 다른 딜레이 셀(102~107)도 이와 동일한 내부 구조를 가질 수 있다.

- [0050] 도 5를 참조하면, 딜레이 셀(101)은 제1 딜레이 라인(11), 제2 딜레이 라인(21) 및 앤드 게이트(31)를 포함한다. 제1 딜레이 라인(11)은 입력 받은 스텝 전압을 예를 들어 시간 τ만큼 지연시켜 출력하고, 제2 딜레이 라인(21)은 제1 딜레이 라인(11)으로부터 입력 받은 전압을 다시 시간 τ만큼 지연시켜 V<sub>out</sub>으로서 출력한다.

- [0051] 앤드 게이트(31)는 제1 딜레이 라인(11)에 입력되는 스텝 전압과, 제2 딜레이 라인(21)에 입력되는 전압을 AND 연산하여  $V_{\text{SWITCH}}$ 로서 출력한다. 그리고 제1 딜레이 라인(11)과 제2 딜레이 라인(21)은 각각 튜닝 전압  $V_{\text{TUNE}}$ 을 입력 받을 수 있으며, 이 튜닝 전압  $V_{\text{TUNE}}$ 은 각 딜레이 라인(11, 21)의 시간 지연(time delay)을 튜닝하는 역할을 한다.

- [0052] 딜레이 셀(100)은 입력 받은 스텝 전압을 소정 시간만큼 지연시켜  $V_{out}$ 으로서 출력하고, 이와 함께 상기 스텝 전압을 구형파 전압으로 전환하여  $V_{SWITCH}$ 로서 출력하는 역할도 한다. 이를 위해 딜레이 셀(100)에 포함되어 있는 딜레이 라인은 인버터를 기반으로 하여 이루어질 수 있다.

- [0053] 도 6은 도 4에 나타낸 복수 개의 딜레이 셀 중 제1 딜레이 셀을 나타낸 도면이고, 도 7은 도 6에 나타낸 딜레이 셀의 각 구역에 대한 타이밍 다이아그램이다.

- [0054] 도 6에 나타낸 바와 같이, 제1 딜레이 셀(101)의 딜레이 라인(11, 21)은 인버터(11-1, 21-1)를 포함하며, 인버터(11-1, 21-1)의 전파 지연(propagation delay)을 조정하기 위하여 NMOS 트랜지스터(11-2, 21-2)가 인버터(11-1, 21-1)에 연결될 수 있다.

- [0055] 도 7(a)는 제1 딜레이 셀(101)의 제1 딜레이 라인(11)에 입력되는 스텝 전압을 나타낸 것이다. 도 7(a)와 같은 스텝 전압이 제1 딜레이 라인(11)에 입력될 경우, 제1 딜레이 라인(11)의 제1 인버터(11-1)는 상기 스텝 전압을 시간 τ만큼 지연 및 반전시켜 도 7(a)<sub>1</sub>과 같은 전압 파형을 출력한다.

- [0056] 계속해서, 도 7(a)<sub>1</sub>과 같은 전압 과형이 제1 딜레이 셀(101)의 제2 딜레이 라인(21)에 입력될 경우, 제2 딜레이라인(21)의 제2 인버터(21-1)는 상기 전압 과형을 다시 τ만큼 지연 및 반전시켜 도 7(b)'와 같은 전압 과형, 즉 도 7(a)에 비해 2 τ만큼 지연된 스텝 전압을  $V_{out}$ 으로서 출력한다. 그리고 이와 같이 제1 딜레이 셀(101)에서 출력하는 스텝 전압  $V_{out}$ 은 제2 딜레이 셀(102)에 입력된다.

- [0057] 제1 딜레이 셀(101)의 앤드 게이트(31)는 제1 딜레이 라인(11)에 입력되는 스텝 전압(도 7(a))과, 제2 딜레이라인(21)에 입력되는 전압(도 7(a)<sub>1</sub>)을 AND 연산하여 도 7(b)와 같은 전압 파형, 즉 지속 시간이 τ인 구형파전압을 V<sub>SWITCH</sub>로서 출력한다. 그리고 이와 같이 제1 딜레이 셀(101)에서 출력하는 구형파 전압 V<sub>SWITCH</sub>은 후술하는트랜지스터(201)의 게이트 전극에 입력된다.

- [0058] 비록 도 6에서는 제1 딜레이 라인(11)이 하나의 인버터(11-1)만을 포함하고, 제2 딜레이 라인(21)도 하나의 인버터(21-1)만을 포함하는 것으로 나타냈지만, 각 딜레이 라인(11, 21)에 포함되는 인버터의 개수는 둘 이상일수 있다. 이때, 둘 이상의 인버터는 서로 케스케이드 결합될 수 있다. 그리고 이와 같이 둘 이상의 인버터가 서

로 케이케이드 결합될 경우에는 제1 딜레이 셀(101)에서 출력하는 스텝 전압  $V_{out}$ 의 온 시점이  $2\tau$ 보다 더 지연되며, 제1 딜레이 셀(101)에서 출력하는 구형파 전압  $V_{swrreg}$ 의 온 시점 역시 동일한 시간만큼 지연될 수 있다.

- [0059] 도 8은 도 4에 나타낸 복수 개의 딜레이 셀 중 제2 딜레이 셀을 나타낸 도면이고, 도 9는 도 8에 나타낸 딜레이 셀의 각 구역에 대한 타이밍 다이아그램이다.

- [0060] 도 8에 나타낸 바와 같이, 제2 딜레이 셀(102)의 딜레이 라인(12, 22)은 인버터(12-1, 22-1)를 포함하며, 인버터(12-1, 22-1)의 전파 지연을 조정하기 위하여 NMOS 트랜지스터(12-2, 22-2)가 인버터(12-1, 22-1)에 연결될수 있다.

- [0061] 도 9(b)'는 제2 딜레이 셀(102)의 제1 딜레이 라인(12)에 입력되는 스텝 전압을 나타낸 것으로서, 이는 도 7(b)'에 나타낸 것과 동일한 것이다. 도 9(b)'와 같은 스텝 전압이 제1 딜레이 라인(12)에 입력될 경우, 제1 딜레이 라인(12)의 제1 인버터(12-1)는 상기 스텝 전압을 시간 τ만큼 지연 및 반전시켜 도 9(b)'ı과 같은 전압 파형을 출력한다.

- [0062] 계속해서, 도 9(b)'₁과 같은 전압 파형이 제2 딜레이 셀(102)의 제2 딜레이 라인(22)에 입력될 경우, 제2 딜레이 라인(22)의 제2 인버터(22-1)는 상기 전압 파형을 다시 τ만큼 지연 및 반전시켜 도 9(c)'와 같은 전압 파형, 즉 도 9(b)'에 비해 2 τ만큼 지연된 스텝 전압을 V<sub>out</sub>으로서 출력한다. 그리고 이와 같이 제2 딜레이 셀(102)에서 출력하는 스텝 전압 V<sub>out</sub>은 제3 딜레이 셀(103)에 입력된다.

- [0063] 제2 딜레이 셀(102)의 앤드 게이트(32)는 제1 딜레이 라인(12)에 입력되는 스텝 전압(도 9(b)')과, 제2 딜레이라인(22)에 입력되는 전압(도 9(b)'₁)을 AND 연산하여 도 9(c)와 같은 전압 파형, 즉 지속 시간이 τ이되 도 7(b)에 나타낸 구형파 전압에 비해 시간 2 τ만큼 지연된 구형파 전압을 V<sub>SWITCH</sub>로서 출력한다. 그리고 이와 같이제2 딜레이 셀(102)에서 출력하는 구형파 전압 V<sub>SWITCH</sub>은 트랜지스터(202)의 게이트 전극에 입력된다.

- [0064] 비록 도 8에서는 도 6과 마찬가지로 제1 딜레이 라인(12)이 하나의 인버터(12-1)만을 포함하고, 제2 딜레이 라인(22)도 하나의 인버터(22-1)만을 포함하는 것으로 나타냈지만, 각 딜레이 라인(12, 22)에 포함되는 인버터의 개수는 둘 이상일 수 있다. 이때, 둘 이상의 인버터는 서로 케스케이드 결합될 수 있다. 이와 같이 둘 이상의 인버터가 서로 케이케이드 결합될 경우에는 제2 딜레이 셀(102)에서 출력하는 스텝 전압 V₀ut의 온 시점이 2 τ 보다 더 지연되며, 제2 딜레이 셀(102)에서 출력하는 구형과 전압 VՏΨΙΤCH의 온 시점 역시 동일한 시간만큼 지연될수 있다.

- [0065] 또한, 상술한 바와 마찬가지의 방식으로, 제3 딜레이 셀(103)은 제2 딜레이 셀(102)로부터 입력 받은 스텝 전압을 소정 시간(예를 들어, 2τ)만큼 지연시켜 제4 딜레이 셀(104)에 출력하고, 이와 함께 제2 딜레이 셀(102)로부터 입력 받은 스텝 전압을 구형파 전압 V<sub>SWITCH</sub>으로 전환하여 트랜지스터(203)의 게이트 전국에 입력시킨다. 즉, 본 발명에서 각각의 딜레이 셀(101~106)은 입력 받은 스텝 전압을 소정 시간(예를 들어, 2τ)만큼 지연시켜이웃하는 딜레이 셀(102~107)에 지연된 스텝 전압을 출력하도록 구성된다.

- [0066] 다만, 도 4에서 가장 우측에 위치한 제7 딜레이 셀(107)은 제6 딜레이 셀(106)로부터 입력 받은 스텝 전압을 구형파 전압 V<sub>SWITCH</sub>으로 전환하여 트랜지스터(207)의 게이트 전극에 입력시키기만 할 뿐, 제6 딜레이 셀(106)로부터 입력 받은 스텝 전압을 소정 시간(예를 들어, 2τ)만큼 지연시켜 다른 딜레이 셀에 출력하지는 않는다. 즉, 본 발명에서 각각의 딜레이 셀(102~107)은 상기 지연된 스텝 전압을 이웃하는 딜레이 셀(101~106)로부터 입력받는다.

- [0067] 도 10은 도 4에 나타낸 초광대역 펄스 생성 장치의 각 구역에 대한 타이밍 다이아그램이다. 보다 구체적으로, 도 10(a)는 제1 딜레이 셀(101)에 입력되는 스텝 전압의 타이밍 다이아그램이고, 도 10(b)~(h)는 각 딜레이 셀(101~107)에서 출력하는 구형과 전압의 타이밍 다이아그램이며, 도 10의 V<sub>OUT</sub>은 후술하는 출력단(400)에서 출력하는 삼각형의 포락선 펄스에 대한 타이밍 다이아그램이다.

- [0068] 도 10(b)~(h)에서 알 수 있듯이, 각 딜레이 셀(101~107)에서 출력하는 구형파 전압은 2τ만큼의 지연 시간이 존 재한다. 그리고 도 10(b)~(h)에 나타낸 구형파 전압은 복수 개의 트랜지스터(200: 201~207)에 개별적으로 인가된다.

- [0069] 복수 개의 트랜지스터(200)는 복수 개의 딜레이 셀(100) 각각에 의해 전환된 구형파 전압을 입력 전압으로 하여 전류를 생성한다. 여기서, 복수 개의 트랜지스터(200)는 복수 개의 딜레이 셀(100)과 1:1로 대응되도록 연결될수 있다. 이에 따라, 제1 딜레이 셀(101)에서 출력하는 구형파 전압은 제1 트랜지스터(201)의 게이트 전국에 입력될수 있다. 그리고 제1 트랜지스터(201)가 이와 같이 상기 구형파 전압을 입력 받을 경우에는, 제1 트랜지스터(201)의 드레인 전국과 소스 전국 사이에 채널이 형성되어 일정 크기의 전류가 흐를 수 있게 된다. 이와 마찬가지로, 그 외 다른 딜레이 셀(102~107)에서 출력하는 구형파 전압은 트랜지스터(202~207)의 게이트 전국에 입력될수 있다. 그리고 트랜지스터(202~207)가 이와 같이 상기 구형파 전압을 입력 받을 경우에는, 트랜지스터(202~207)의 드레인 전국과 소스 전국 사이에 채널이 형성되어 전류가 흐를 수 있게 된다.

- [0070] 이때, 복수 개의 트랜지스터(200) 각각에서 생성되는 전류의 크기는 모두 다를 수 있다. 예를 들어, 복수 개의 트랜지스터(200) 중 중앙에 배치되는 트랜지스터(204)는 가장 큰 전류를 생성하고, 상기 중앙을 기준으로 양측에 배치되는 트랜지스터(201, 202, 203, 205, 206, 207)는 상기 중앙에서 상기 양측으로 갈수록 선형적으로 감소된 크기의 전류를 생성할 수 있다. 이는 도  $10(b)\sim(h)$ 에 나타낸 바와 같은  $2\tau$ 만큼의 시간 간격으로 발진기(300)에 서로 다른 크기의 전류를 공급하여, 발진기(300)의 진폭 조정을 통해 삼각형의 포락선 펄스를 생성하기위함이다.

- [0071] 여기서, 복수 개의 트랜지스터(200) 중 중앙에 배치되는 트랜지스터(204)가 가장 큰 전류를 생성하도록 하기 위하여 상기 트랜지스터(204)의 크기를 가장 크게 하는 것이 바람직하다. 그리고 상기 중앙을 기준으로 상기 양측에 배치되는 트랜지스터(201, 202, 203, 205, 206, 207)는 상기 중앙에서 양측으로 갈수록 트랜지스터의 크기를 선형적으로 감소시킴으로써, 상기 중앙에서 상기 양측으로 갈수록 선형적으로 감소된 크기의 전류를 생성하도록하는 것이 바람직하다.

- [0072] 보다 구체적으로, 복수 개의 트랜지스터(200) 중 중앙에 배치되는 트랜지스터(204)가 가장 큰 전류를 생성하도록 하기 위한 방안 중 하나로, 상기 트랜지스터(204)의 채널 길이(L) 대비 채널 폭(W)을 다른 트랜지스터(201, 202, 203, 205, 206, 207)의 채널 길이(L) 대비 채널 폭(W)에 비해 더 크게 할 수 있다. 즉, 중앙에 배치되는 트랜지스터(204)의 W/L를 다른 트랜지스터(201, 202, 203, 205, 206, 207)의 W/L에 비해 더 크게 할 수 있는 것이다. 이때, 상기 중앙을 기준으로 상기 양측에 배치되는 트랜지스터(201, 202, 203, 205, 206, 207)는 상기 중앙에서 양측으로 갈수록 트랜지스터의 채널 길이(L) 대비 채널 폭(W)을 선형적으로 감소시킴으로써, 상기 중앙에서 상기 양측으로 갈수록 선형적으로 감소된 크기의 전류를 생성하도록 할 수 있다.

- [0073] 더불어 채널 길이(L)는 모든 트랜지스터(200)에서 동일하게 제작될 수 있으며, 따라서 이 경우에는 트랜지스터 (200)의 채널 폭(W)에 대략 비례해서 각각의 트랜지스터(200)에서 생성되는 전류의 크기가 결정되게 된다. 예를 들어, 모든 트랜지스터(200)의 채널 길이(L)가 동일한 경우, 트랜지스터 폭의 공칭 크기(nominal size)가 12 μm 일 경우, 도 4에서 중앙에 배치된 제4 트랜지스터(204)의 크기는 공칭 크기의 3.5배로 구성하고, 그 양측에 배치된 제3 트랜지스터(203) 및 제5 트랜지스터(205)는 공칭 크기의 2.5배로 구성할 수 있다. 그리고 제2 트랜지스터(202) 및 제6 트랜지스터(206)는 공칭 크기의 1.5배로 구성하고, 최외각에 배치된 제1 트랜지스터(201) 및 제7 트랜지스터(207)의 크기는 공칭 크기의 0.5배로 구성할 수 있다. 이와 같이 복수 개의 트랜지스터(200) 크 기를 중앙에서 양측으로 갈수록 선형적으로 감소하도록 구성할 경우, 출력단(400)에서 출력되는 삼각형 포락선 필스의 필스 스펙트럼은 향상된 사이드로브 억압 기능을 제공할 수 있게 된다.

- [0074] 다만, 삼각형의 포락선 펄스를 생성할 경우에는 이와 같이 복수 개의 트랜지스터(200) 크기를 중앙에서 양측으로 갈수록 선형적으로 감소하도록 구성하는 것이 바람직하지만, 반드시 선형적으로 감소하도록 구성하는 것만으로 한정되는 것은 아니며, 복수 개의 트랜지스터(200)의 크기는 얼마든지 다양하게 구성할 수 있다.

- [0075] 한편, 사인형의 포락선 펄스를 생성하고자 할 경우에는, 복수 개의 트랜지스터(200) 각각에서 생성되는 전류의 크기를, 상기 삼각형의 포락선 펄스를 생성하는 경우와는 달리 구성할 수 있다. 따라서, 이 경우에는 복수 개의 트랜지스터(200) 각각의 크기를 도 4에 도시된 바와는 달리 정할 것이 요구된다. 그리고 직사각형의 포락선 펄스를 생성하고자 할 경우에는, 복수 개의 트랜지스터(200) 각각에서 생성되는 전류의 크기를 모두 동일하게 할 수 있다. 따라서, 이 경우에는 복수 개의 트랜지스터(200) 크기를 모두 동일하게 할 수 있다.

- [0076] 발진기(300)는 도 2에 관해 상술한 바와 같이 저항(R<sub>T</sub>), 인덕터(L<sub>T</sub>) 및 커패시터(C<sub>T</sub>)가 서로 병렬 연결된 RLC 탱크를 기반으로 하여 구성될 수 있으며, 저항(R<sub>T</sub>), 인덕터(L<sub>T</sub>) 및 커패시터(C<sub>T</sub>)는 발진기(300)의 동작 전압원(V<sub>D</sub>D)의 동작 전압에 의해 동작할 수 있다.

- [0077] 발진기(300)는 복수 개의 트랜지스터(200) 각각에 의해 생성된 전류를 전달 받아 지수함수적으로 감쇠되는 복수 개의 정현파 전압을 생성한다. 구체적으로, 도 10에 나타낸 0~2  $\tau$ 의 시간 구간에서는 트랜지스터 공칭 크기의 0.5배에 상응하는 전류가 발진기(300)에 전달되어 도 3ⓒ와 같이 발진기(300) 출력 전압의 진폭이 조정되고, 2  $\tau$ ~4 $\tau$ 의 시간 구간에서는 트랜지스터 공칭 크기의 1.5배에 상응하는 전류가 발진기(300)에 전달되어 도 3億와 같이 발진기(300) 출력 전압의 진폭이 조정될 수 있다. 그리고 이와 같은 방식으로 0~14 $\tau$ 의 시간 구간에서 발진기(300) 출력 전압의 진폭이 조정될 수 있다.

- [0078] 출력단(400)은 복수 개의 트랜지스터(200) 및 발진기(300)와 연결되어 있으며, 이에 따라 출력단(400)에서는 상기 발진기(300)에서 생성되는 복수 개의 정현과 전압을 합성하여 삼각형의 포락선 펄스를 출력하게 된다. 출력 단(400)에서 출력하는 삼각형의 포락선 펄스는 도 10에 나타낸 Vour과 같은 형태를 갖게 된다.

- [0079] 한편, 출력단(400)에는 삼각형의 포락선 펄스에서 DC 성분을 제거하기 위하여 바이패스 커패시터(C<sub>BYPASS</sub>)가 연결될 수 있다. 보다 구체적으로, 바이패스 커패시터(C<sub>BYPASS</sub>)는 발진기(300)와 출력단(400) 사이에 연결될 수 있으며, 고주파 대역의 통과 특성으로 인해 삼각형의 포락선 펄스에서 DC 성분뿐 아니라 저주파 성분의 차단 역할도수행할 수 있다.

- [0080] 한편, 출력단(400)에서 출력하는 삼각형의 포락선 펼스는 안테나를 통해 송출된다. 이때, 안테나의 임피던스가 예를 들어 50요일 경우, 발진기(300)를 구성하는 저항(R₁), 인덕터(L₁) 및 커패시터(C₁)의 합성 임피던스 역시 50요으로 매칭시킴으로써 안테나의 펄스 송출 효율을 최대로 할 수 있다.

- [0081] 도 11은 도 4에 나타낸 장치를 통해 생성한 초광대역 펄스의 시뮬레이션 결과이다. 도 11의 시뮬레이션 결과는 900mV의 동작 전압(Vpp)에서 수행한 것으로서, 초광대역 펄스의 피크-대-피크(peak-to-peak) 전압 Vpp는 577mV로 측정되었고, 초광대역 펄스의 진폭은 중앙을 기준으로 양측으로 갈수록 선형적으로 감소하였다. 그리고 초광대역 펄스의 유효 펄스 폭(effective pulse width) tpulse는 1.6ns로 측정되었다.

- [0082] 도 12는 도 4에 나타낸 장치를 안테나의 임피던스와 매칭시킨 시뮬레이션 결과이다. 발진기(300)를 구성하는 저항(R<sub>T</sub>), 인덕터(L<sub>T</sub>) 및 커패시터(C<sub>T</sub>)의 합성 임피던스를 조정하여 안테나의 임피던스와 동일하게 50요으로 매칭시켰으며, 상기 합성 임피던스를 조절하여 펄스 스펙트럼의 중심 주과수가 4GHz인 지점에서 안테나와 임피던스 매칭이 이루어지도록 하였다. 즉, 발진기(300)를 구성하는 저항(R<sub>T</sub>), 인덕터(L<sub>T</sub>) 및 커패시터(C<sub>T</sub>)의 합성 임피던 스를 조정하는 것만으로도 초광대역 펄스 스펙트럼의 중심 주과수를 가변시킬 수 있으며, 이에 따라 원하는 형태의 펄스를 손쉽게 생성할 수 있게 된다. 또한, 별도의 임피던스 매칭 회로를 구비하지 않더라도 발진기(300)를 통해 안테나와의 임피던스 매칭 역시 손쉽게 수행할 수 있다.

- [0083] 한편, 도 13은 도 11에 나타낸 초광대역 펄스의 전력 스펙트럼 밀도에 관한 시뮬레이션 결과이다. 도 13에 나타 난 바와 같이, 메인로브의 중심 주파수는 4GHz이며, 이때의 전력 레벨(power level)은 -60.39dBm으로 나타났다. 그리고 제1 사이드로브의 중심 주파수는 3.1GHz이며, 이때의 전력 레벨은 -81.8dBm으로 나타났다. 도 13에 표시되어 있는 점선은 FCC 스펙트럼 마스크를 나타낸 것으로서, 초광대역 펄스의 전력 스펙트럼 밀도는 FCC 스펙트럼 마스크를 넘지 않아야 한다. 도 13에 의하면, 도 11에서 생성한 초광대역 펄스의 전력 스펙트럼 밀도는 FCC 스펙트럼 마스크에 부합한다는 것을 알 수 있으며, 특히 사이드로브가 FCC 스펙트럼 마스크를 넘지 않도록 적절히 억압되어 있다는 것을 알 수 있다.

- [0084] 이상과 같이 본 발명은 비록 한정된 실시예와 도면에 의해 설명되었으나, 본 발명은 상기의 실시예에 한정되는 것이 아니라 본 발명이 속하는 분야에서 통상의 지식을 가진 자라면 이러한 기재로부터 다양한 수정 및 변형이 가능하다. 따라서, 본 발명의 기술적 사상은 청구범위에 의해서만 파악되어야 하고, 이의 균등 또는 등가적 변형 모두는 본 발명의 기술적 사상의 범주에 속한다고 할 것이다.

#### 부호의 설명

[0085] 11, 12: 제1 딜레이 셀

11-1, 21-1: 인버터

11-2, 21-2: NMOS 트랜지스터

21, 22: 제2 딜레이 셀

### 31, 32: 앤드 게이트

100(101, 102, 103, 104, 105, 106, 107): 딜레이 셀 200(201, 202, 203, 204, 205, 206, 207): 트랜지스터

300: 발진기 400: 출력단

### 도면

도면5

## 도면8

102

(b)'

(b)'<sub>1</sub>

(c)'

(c) \_\_\_\_\_