출원번호 : 10-2022-0048777 (출원일: 2022-04-20)

등록번호 : 10-2421173 (등록일: 2022-07-11)

특허권자 : 충남대학교산학협력단

요약 : 열처리를 가하기 전 니켈과 게르마늄 층 사이에 터븀 층을 삽입한 뒤, 열처리를 가하여 반도체 소자의 합금 콘택을 형성함으로써 접촉저항을 감소시킬 수 있다.

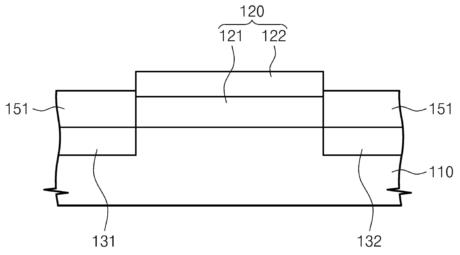

대표청구항 : 기판에 소스 및 드레인 영역과 게이트 전극을 형성하는 단계; 상기 소스 및 드레인 영역 상에 터븀(Tb) 층을 적층시키는 단계; 상기 터븀 층 상에 금속 층을 적층시키는 단계; 및상기 터븀 층과 상기 금속 층이 적층된 상기 기판을 열처리 하는 단계;를 포함하되,상기 소스 및 드레인 영역은 게르마늄층으로 구성되고,상기 터븀 층 상에 금속 층을 적층시키는 단계는, 상기 터븀 층 상에 니켈(Ni) 층을 적층시키는 단계; 및상기 니켈 층 상에 타이타늄 나이트라이드(TiN) 층을 적층시키는 단계; 를 포함하는 반도체 소자의 콘택 형성 방법.

상세링크 : http://newsd.wips.co.kr/wipslink/api/dkrdshtm.wips?skey=3522302001479